Welcome to the YASEP's website !

version 2016/08/07 - standalone/noJS

What is the YASEP ?

The acronym "YASEP" means "Yet Another Small Embedded Processor".

It's a family of original, Free,

configurable (16-bit or 32-bit) microcontroller cores,

meant to be quite small and as simple as possible (well, that's the original idea).

The YASEP is also an experiment in computer design methodologies.

The architecture exists in the form of a standalone HTML5 application that contains (and generates) VHDL source code,

an architecture simulator,

an assembler, a disassembler, a SPI memory Flasher, a manual, configuration tools, and much more!

Every part is integrated in the others (and vice versa), so the whole remains (mostly) coherent, easy to use and

quick to develop, fix and maintain. By extension, the YASEP is also a testbed for a modular toolset

(using the dynamic YGWM framework) that will be re-used for other projects,

in particular to design other CPU architectures such as F-CPU.

You will find some background on this project in the application's documentation,

in the archives,

in the blog and in these presentations:

EHSM2012 (english)

and JMLL2012 (french).

Happy clicking !

yg

Play and download

Choose your pill: the red-blue or the blue-red ?

- The last stable version is from the YASEP2013 development cycle.

It is the least broken release yet (enough tools are functional for simulation) but there are some shortcomings

and the instruction set has changed since. In other words : it works but it's obsolete.

- The more recent version is from the YASEP2014 development cycle.

The instruction set has been totally revamped but the tools are badly broken. It's provided as an overview of what's

to come for YASEP2015/16 (such as the Flash feature).

You can download the whole YASEP web application (source code, pages, documentation, tools, etc.)

from the archives or from the application's menu,

as a single file in .tar.bzip2 format. You can test the YASEP at home and play

with the source code at will.

Note : if you want to use certain features

(like file save/load), you'll need to modify your computer

configuration. Install Apache under GNU/Linux,

or EasyPHP under MS Windows. The SPI Flash tool needs

a Raspberry Pi and some circuitry.

The YASEP's features and characteristics

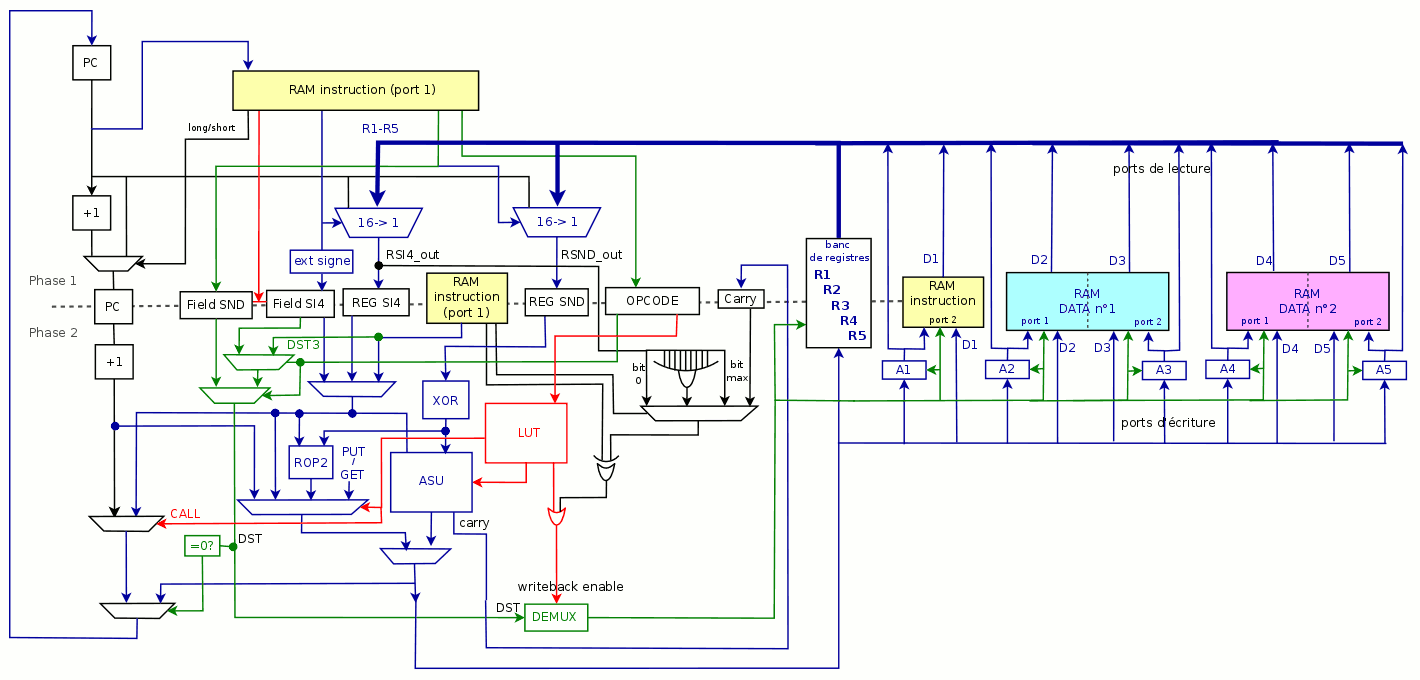

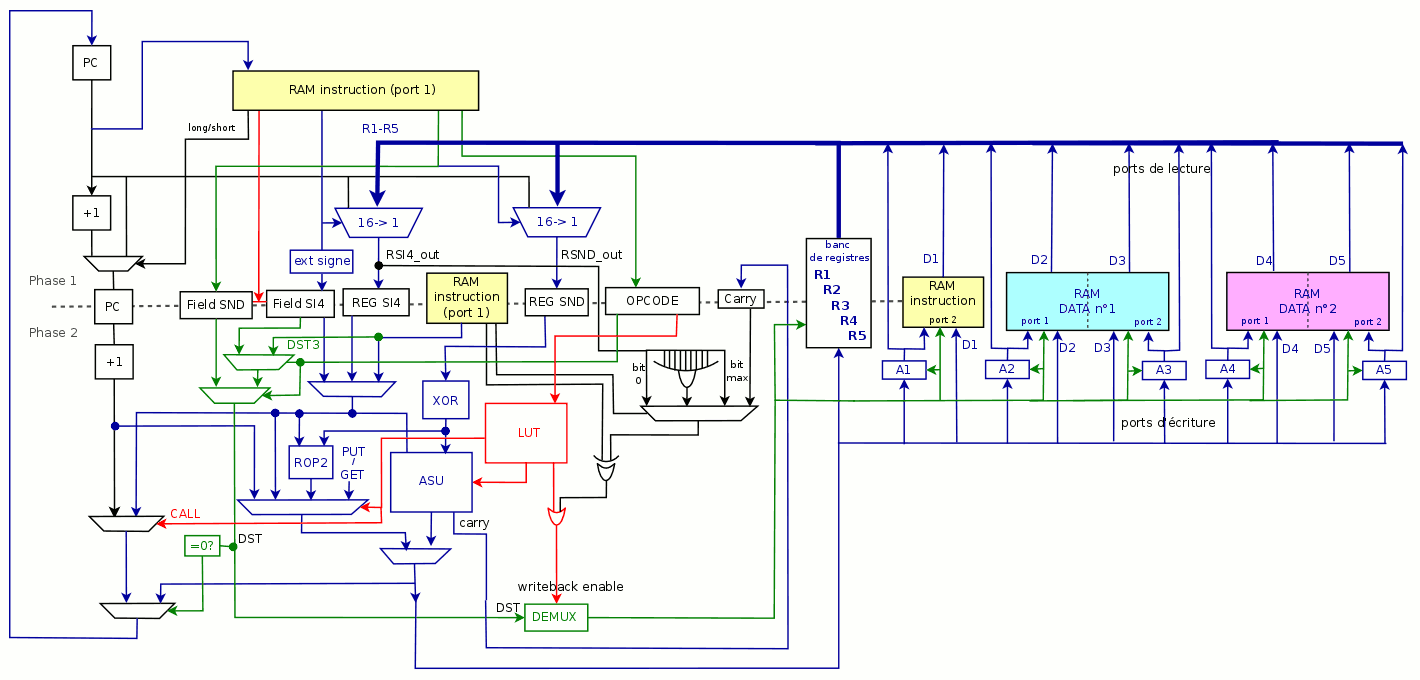

- Single-issue, pipelined, in-order, RISC architecture with 16 "registers" (including PC) and register-mapped memory.

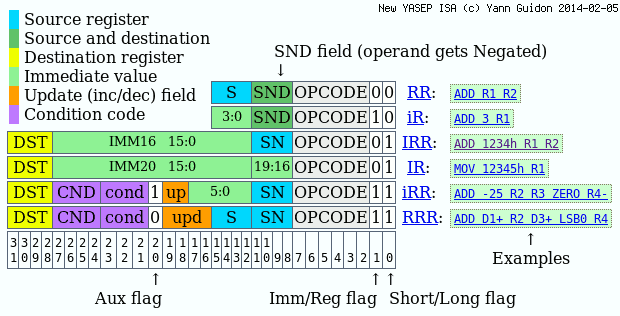

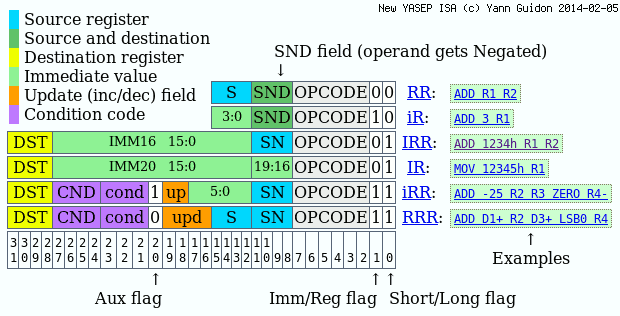

- Orthogonal 16-bit instructions : 51 opcodes with an optional 16-bit additional immediate word or extended word

- Compact instruction words with short and long immediate, 2, 3 or 4 register operands.

- Configurable with either a 16 or 32-bit wide datapath with/without several features (memory, multiply...).

- Register-mapped memory that increases data memory bandwidth :

an instruction can trigger up to 3 data memory accesses, instead of 1 for a typical load-store architecture.

- The abstract architecture is specified with JavaScript+HTML,

which generates the VHDL source code (suitable for FPGA and ASIC). Actel's ProASIC3

is the targeted technology, other brands will come later.

- The YASEP is Free Hardware Design ! It is available under the Affero GPL license.

All the code is original and copyrighted by myself. Please contact me for custom licensing or special development.

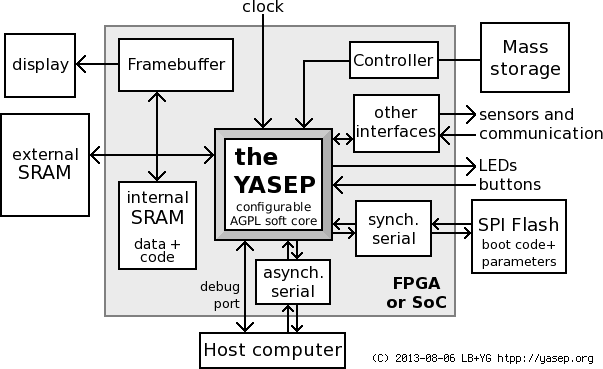

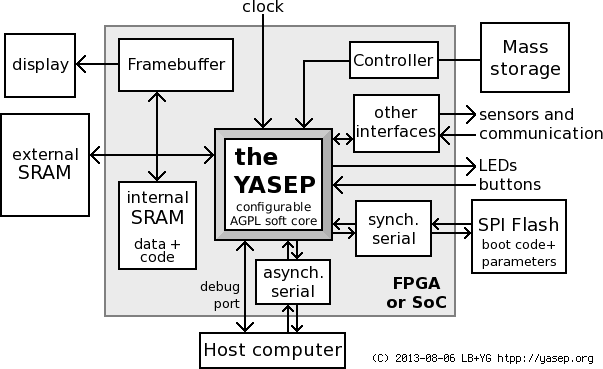

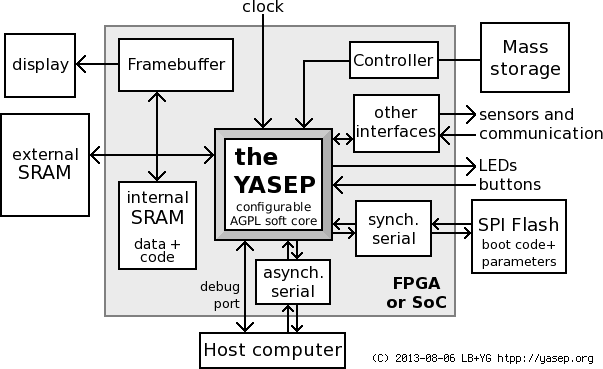

The following diagram shows all the details of the structure of a typical microYASEP implementation:

Milestones

However the YASEP project is still not considered ready. The new instruction set format has broken many tools that need to be rewritten

and cleaned up. The whole code base is being reviewed, starting from the YGWM framework that has grown beyond expectations.

YASEP2014 obsoletes the previous architectures and should not change radically again. But time was devoted to other work (such as PCB)

and the YASEP2015 milestone is late.

A lot of work remains...

The YASEP on the web

- The YASEP has its own website : yasep.org. You are probably reading this there.

- Some mirrors exist as well, and may be out of synch. The one at seul.org vanished in early 2010

due to technical problems, after 10 years of great service. Another mirror

is now available from TuxFamily. Thank you !

- Another mirror, courtesy of Troy

- The old versions of the site are kept separate in archives (for historical reasons).

- A blog provides less-technical informations and some human interaction.

- The YASEP is also on facebook

- A few project pages have been created on Hackaday.io:

The YASEP, microYASEP,

YGWM and the Discrete YASEP

Other websites

- The Colibri is a little cost-effective FPGA module

(the successor of the FoxVHDL board without the VGA output). Among other things, it is ideal to develop and prototype the YASEP.

- I also helped to define the second version of this nice prototyping board designed by Miguel Angel Ajo Pelayo.

- A modular assembler (written in C) is being

developped by DeforaOS and support for the YASEP architecture started in september 2011.

- F-CPU is where it all started (more or less)

- Wikipedia has an interesting list of soft cores.

- YGWM is the windowing toolkit that was developed for this website. It now has its own indepedent website where more resources will be moved.

- HTTaP is the protocol that the HTML5 modules use to communicate over IP with software or hardware emulation targets.